# **Detector Support Group**

We choose to do these things "not because they are easy, but because they are hard". Weekly Report, 2021-11-17

# <u>Summary</u>

### <u>Hall A – SoLID</u>

Mary Ann Antonioli, Pablo Campero, Brian Eng, Mindy Leffel, and Marc McMullen

- Wiring instrumentation racks #1 and #2

- ★ Wired 17 signal conditioners and three terminal strip groups for temperature sensors

### <u>Hall B – RICH-II</u>

Mary Ann Antonioli, Peter Bonneau, Pablo Campero, Brian Eng, George Jacobs, Tyler Lemon, and Marc McMullen

- Debugging failed FPGA Command Engine response timeout during testing of SHT35 sensor board using defective sensor

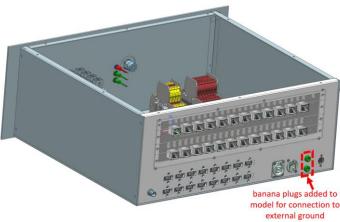

- Added two banana plugs to hardware interlock chassis for connecting RJ45 port shields to an external ground

NX-12 model of hardware interlock chassis with banana plugs

• Completed fabrication drawings for hardware interlock chassis

#### <u>Hall C – NPS</u>

Mary Ann Antonioli, Peter Bonneau, Aaron Brown, Pablo Campero, Brian Eng, George Jacobs, Mindy Leffel, Tyler Lemon, and Marc McMullen

- Revised 36x30 PbWO<sub>4</sub> crystal array model: added polyethylene enclosure and aluminum stand

- Conducted thermal analysis with 22°C ambient temperature outside of the enclosure, 18°C ambient temperature inside of the enclosure, and a heat load of 0.5 W applied to the rear face of each crystal

- ★ Maximum crystal temperature: ~17.8°C

#### Detector Support Group We choose to do these things "not because they are easy, but because they are hard". Weekly Report, 2021-11-17

Screenshot of new PbWO4 crystal array model with front wall of enclosure removed

- Researching conducting Ansys thermal simulations and exporting results to CSV file using Python scripting

- ★ Able to export overall minimum, maximum, and average temperature investigating how to export temperature probe values

- Completed hall temperature and humidity tab in LabVIEW hardware monitoring program

- Developing monitor voltage, current, and power status Phoebus screen

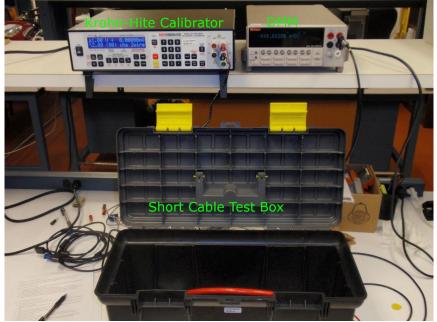

- Conducting high voltage supply cable voltage drop testing: 6 of 36 channels tested

High voltage supply cable voltage drop test station

• Worked on ESR foil pre-shaping – 220 of 600 completed (~37%)

## EIC

#### <u>Pablo Campero, Brian Eng</u>

- Using Ansys, conducting thermal analysis of Be beam pipe and Barrel L1 Si sensor (with and without PEEK rings)

- Started preparing documentation for long lead procurement of GEM foils

- Only one vendor (CERN) and cost > \$750K; procurement process will be quite long

#### DSG – Cleanroom

#### Marc McMullen

- Flooring contractor has completed large cleanroom floor project

- ★ Facilities management is scheduled to clean the walls and change the filters this week

Completed second half of cleanroom floor